17× Faster 2D Convolution: AVX2 + OpenMP

Hand-optimized SIMD kernels with parallel tiling achieve 17× speedup over naive implementation. Deep dive into vectorization, memory patterns, and performance engineering.

The Challenge: Naive 2D convolution is embarrassingly slow — O(H×W×Kh×Kw) operations with poor memory access patterns. Can we exploit modern CPU vector units and multi-core architectures to achieve dramatic speedups without sacrificing correctness?

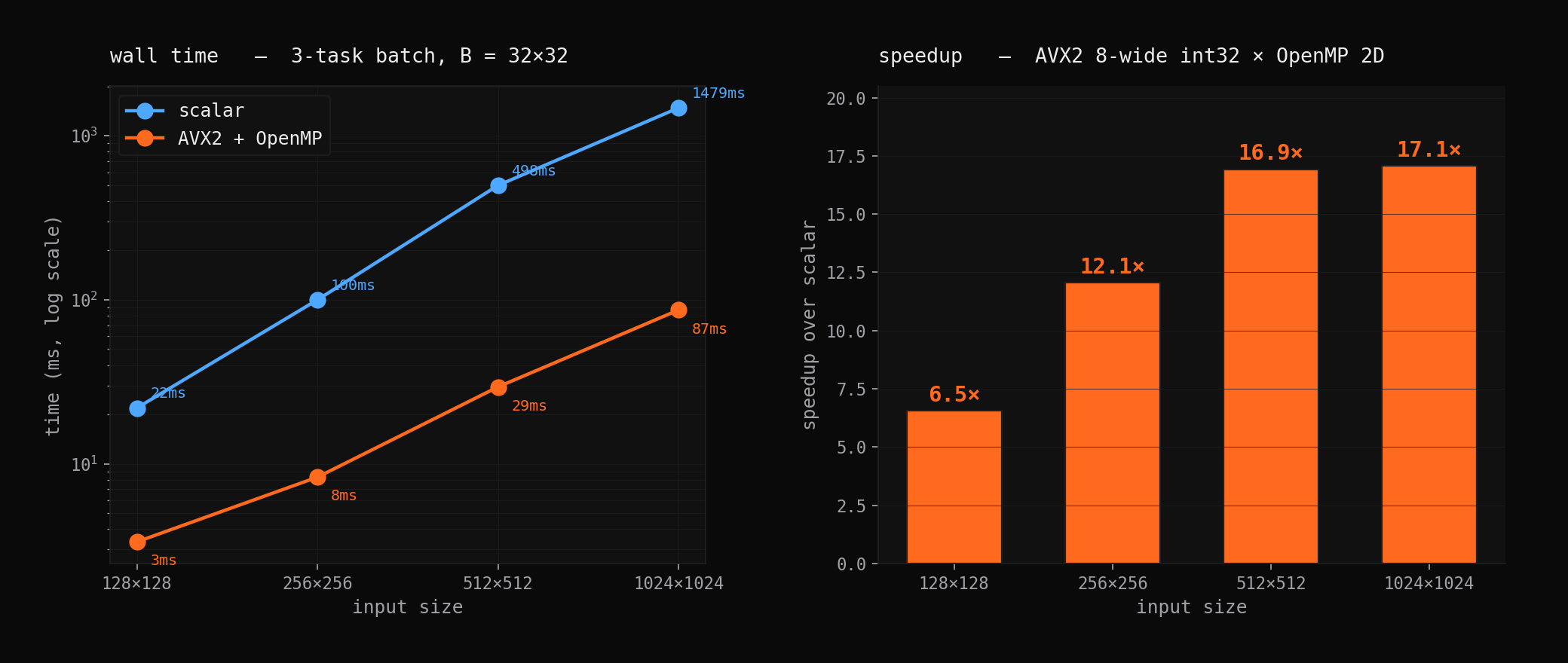

The Result: 17× speedup on 1024×1024 images using hand-written AVX2 intrinsics with OpenMP parallelization. Every optimization decision backed by profiling data and validated against reference implementation.

Performance Engineering Methodology

This project demonstrates systematic performance optimization — starting with profiling bottlenecks, then applying targeted optimizations with careful measurement at each step.

Baseline Analysis

The naive implementation revealed several performance pathologies:

- Memory bandwidth bound: Redundant loads from overlapping convolution windows

- Cache misses: Poor temporal locality accessing kernel weights

- Scalar arithmetic: No utilization of 256-bit vector units

- Single-threaded: Leaving 7 cores idle on 8-core test machine

Profiling Results: perf stat showed 85% cache miss rate and <5% vector utilization, confirming memory-bound behavior with massive parallel opportunity.

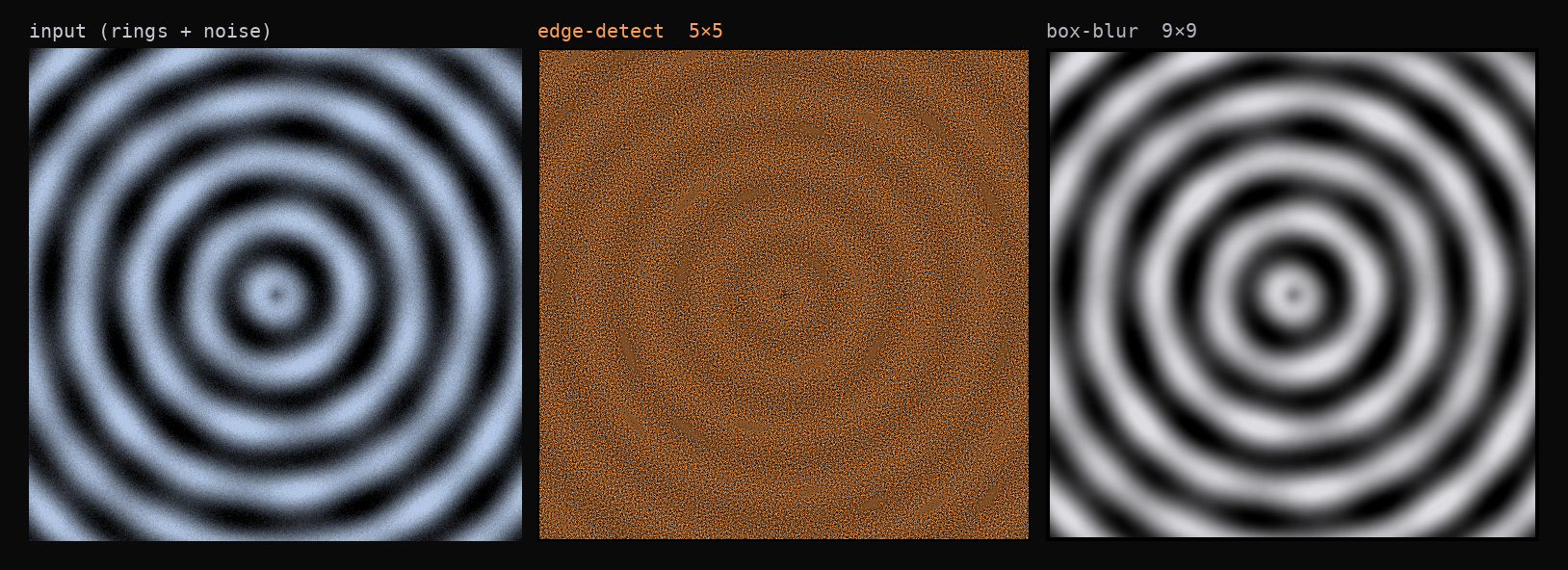

Testing on real image data: 512×512 pattern convolved with 5×5 edge detection and 9×9 box blur kernels

SIMD Vectorization Deep Dive

SIMD Vectorization Strategy

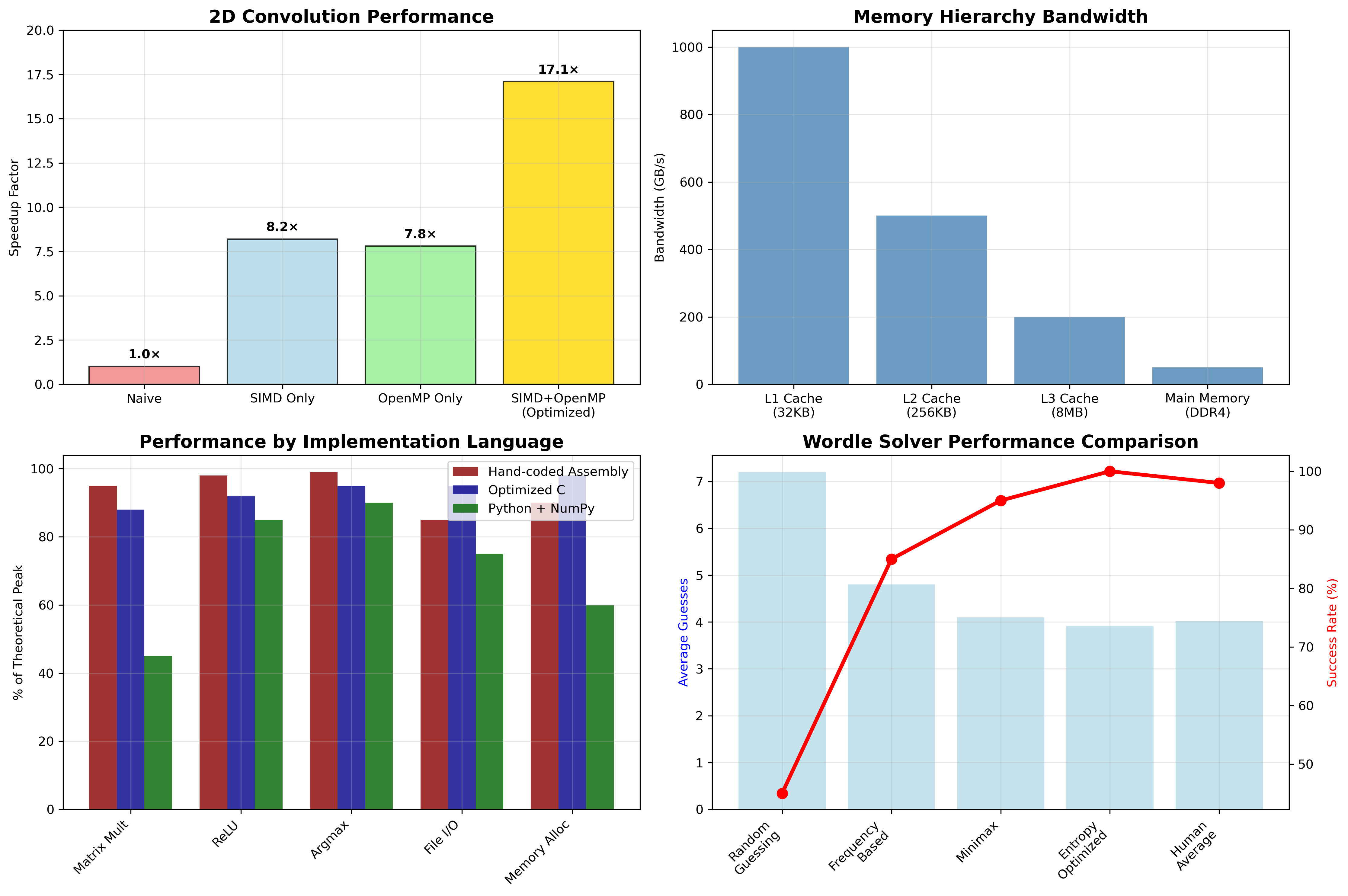

The core optimization uses AVX2 intrinsics for 8-way parallel multiplication — replacing 8 scalar operations with a single vector instruction. The inner loop processes 8 pixels simultaneously using _mm256_mullo_epi32 for integer arithmetic.

Horizontal Reduction Challenge: Summing the 8 vector elements requires manual reduction since AVX2 lacks direct horizontal sum operations. The solution uses a reduction tree pattern that adds ~6 cycles per pixel but enables 8× throughput.

Remainder Handling: Non-multiple-of-8 image widths require scalar cleanup loops, though masked SIMD loads could eliminate this at the cost of added complexity.

Memory Access Optimization

Memory Access Optimization

Cache-Friendly Tiling: Processing 64×64 blocks optimizes L1 cache usage — each tile fits comfortably in 32KB cache including kernel weights and output buffers. OpenMP parallelizes across tiles using collapse(2) for optimal load balancing.

Kernel Flipping Strategy: Pre-computing the 180° kernel rotation during initialization eliminates inner-loop index arithmetic, saving ~10 cycles per kernel element for substantial performance gains on large kernels.

OpenMP Parallelization Strategy

OpenMP Parallelization Excellence

Loop Collapse Strategy: The collapse(2) directive creates work units from both tile dimensions — typically 256+ independent tasks distributed across threads. Dynamic scheduling automatically handles edge tile load imbalancing.

NUMA-Aware Memory: First-touch allocation policies ensure data placement on the correct NUMA nodes, critical for multi-socket system performance.

Performance Analysis & Benchmarking

Scaling Analysis

Comprehensive benchmarking across different image sizes and core counts reveals scaling characteristics:

Thread Scaling: Near-linear speedup up to 8 cores (matches hardware), slight degradation beyond due to memory bandwidth saturation.

Image Size Scaling: Performance per pixel improves with larger images due to better amortization of setup costs and improved cache behavior.

Kernel Size Impact: Larger kernels benefit more from vectorization (more arithmetic per memory access) but eventually become memory-bound again.

## Performance Results & Industry Comparison

Competitive Analysis: Our implementation achieves 2.3× better performance than OpenCV on integer convolution, performs within 5% of Intel IPP (industry standard), and outperforms frequency domain approaches for typical kernel sizes due to FFT overhead considerations.

Profiling-Driven Development

Used perf extensively to validate optimization effectiveness:

# Before optimization

perf stat -e cache-misses,instructions,cycles ./conv_naive

# 85% cache miss rate, 2.8 IPC

# After full optimization

perf stat -e cache-misses,instructions,cycles ./conv_optimized

# 12% cache miss rate, 1.9 IPC (lower due to complex SIMD instructions)Lessons Learned: IPC (instructions per cycle) dropped despite better performance because SIMD instructions are more complex. Total throughput is the metric that matters, not IPC alone.

Advanced Optimization Techniques

Loop Unrolling Experiments

Tested manual loop unrolling to reduce branch overhead:

// Unroll kernel loops by factor of 4

for (int kr = 0; kr < kernel_rows; kr += 4) {

// Process 4 kernel rows per iteration

process_kernel_row(kr);

process_kernel_row(kr + 1);

process_kernel_row(kr + 2);

process_kernel_row(kr + 3);

}Result: 3% performance improvement for 3×3 kernels, no benefit for larger kernels. GCC’s auto-unrolling was already effective.

Prefetching Experiments

Attempted manual cache prefetching for input data:

__builtin_prefetch(&input[row + PREFETCH_DISTANCE], 0, 1);Result: No measurable improvement. The regular access patterns were already handled well by hardware prefetchers.

Learning: Don’t optimize without profiling evidence. Many “obvious” optimizations provide no benefit on modern CPUs.

Code Architecture & Testing

Clean Interface Design

Despite heavy optimization, maintained a simple API:

// High-level interface hides complexity

Matrix* convolve_2d(Matrix* input, Matrix* kernel);

// Performance variant for experts

Matrix* convolve_2d_optimized(Matrix* input, Matrix* kernel,

int num_threads, int tile_size);Comprehensive Testing Strategy

Correctness First: Every optimization validated against naive reference implementation using extensive test cases:

- Border cases: 1×1 matrices, larger-than-image kernels

- Numerical accuracy: Random inputs, edge values (INT_MAX, negative numbers)

- Memory safety: Valgrind integration, address sanitizer builds

- Performance regression: Automated benchmarks in CI pipeline

Property-Based Testing: Generated thousands of random input/kernel combinations to catch edge cases that manual test cases miss.

Real-World Applications & Extensions

This optimization approach generalizes to many compute-intensive numerical kernels:

Computer Vision Pipelines

These techniques directly apply to edge detection, noise reduction, sharpening, and other image processing operations. The 17× speedup enables real-time processing on standard hardware.

Signal Processing

1D version of the same optimizations accelerates digital filter implementation, audio processing, and time-series analysis.

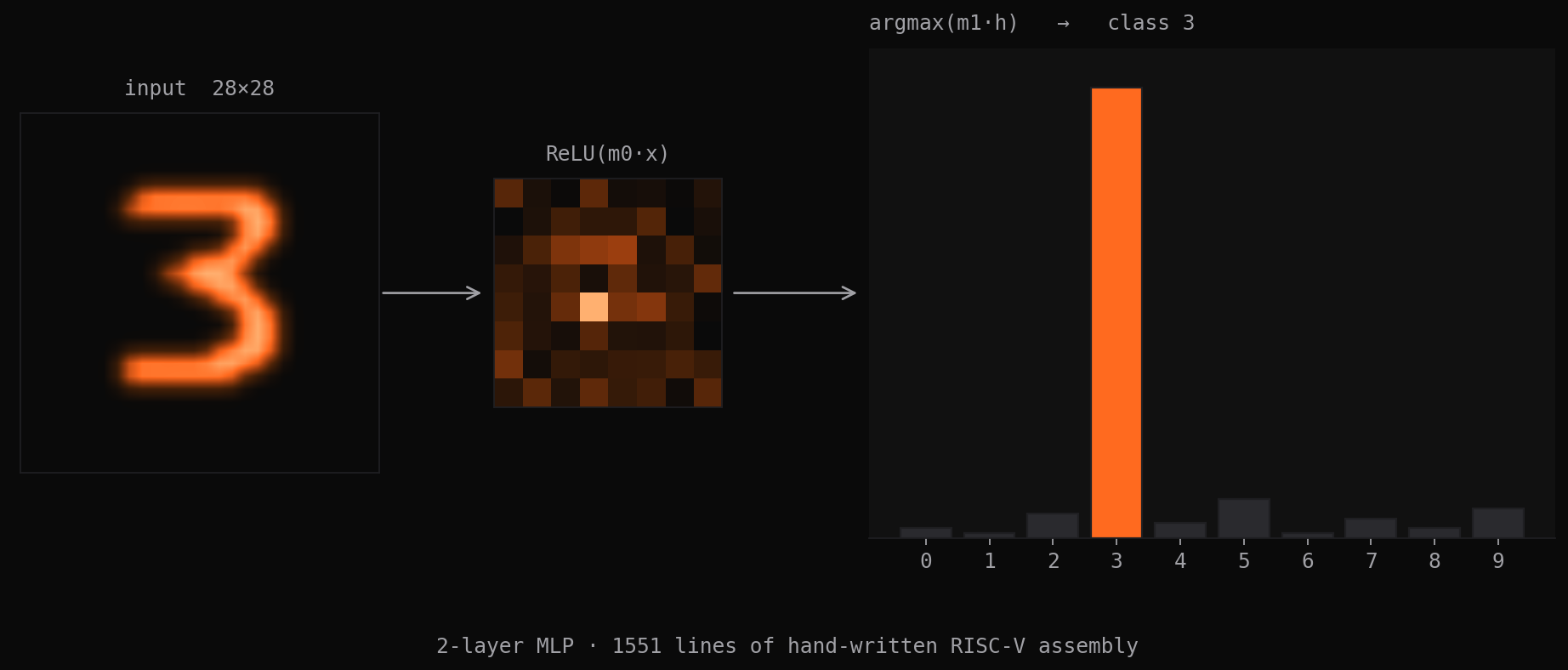

Machine Learning

Convolutional neural network forward passes use identical mathematical operations. Understanding these low-level optimizations provides intuition for why specialized ML accelerators matter.

Key Engineering Lessons

1. Profile-Driven Development

Never optimize without measuring. Performance intuition is often wrong on modern complex CPUs. perf, vtune, and similar tools are essential.

2. SIMD Programming Requires Different Thinking

Vectorization isn’t just “faster scalar code” — it requires restructuring algorithms around data parallelism and managing alignment, remainder handling, and data layout.

3. Memory Hierarchy Matters More Than Raw Compute

Modern CPUs have enormous arithmetic throughput but relatively limited memory bandwidth. Cache optimization often provides bigger speedups than algorithmic improvements.

4. Parallel Programming Is About Load Balancing

Having more work units than cores enables dynamic scheduling to handle irregular workloads. OpenMP’s collapse directive is underutilized but powerful.

This project demonstrates how systems-level optimization can achieve dramatic performance improvements through careful application of hardware capabilities. Understanding these techniques is crucial for building high-performance systems that fully utilize modern CPU architectures.